Some amount (kilobytes or less) is also embedded in practically all modern appliances, toys, etc. Many categories of industrial and scientific subsystems, automotive electronics, and similar embedded systems, contain SRAM which, in this context, may be referred to as ESRAM. The power consumption of SRAM varies widely depending on how frequently it is accessed. Since SRAM requires more transistors per bit to implement, it is less dense and more expensive than DRAM and also has a higher power consumption during read or write access. Performance and reliability are good and power consumption is low when idle. SRAM offers a simple data access model and does not require a refresh circuit. Though it can be characterized as volatile memory SRAM exhibits data remanence. In 1965, Benjamin Agusta and his team at IBM created a 16-bit silicon memory chip based on the Farber-Schlig cell, with 80 transistors, 64 resistors, and 4 diodes.Ĭomparison image of 180 nanometre SRAM cells on a STM32F103VGT6 microcontroller as seen by an optical microscope Characteristics They replaced the latch with two transistors and two resistors, a configuration that became known as the Farber-Schlig cell.

In 1965, Arnold Farber and Eugene Schlig, working for IBM, created a hard-wired memory cell, using a transistor gate and tunnel diode latch.

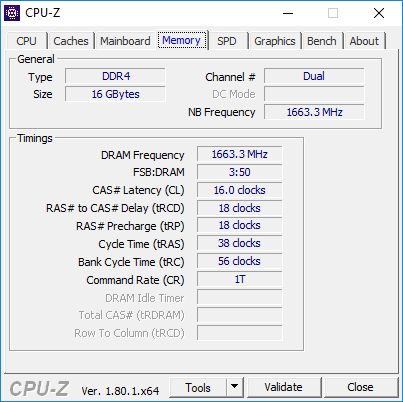

#CPU Z DRAM FREQUENCY DRIVER#

The SRAM was the main driver behind any new CMOS-based technology fabrication process since 1959 when CMOS was invented.

MOS SRAM was invented in 1964 by John Schmidt at Fairchild Semiconductor. Semiconductor bipolar SRAM was invented in 1963 by Robert Norman at Fairchild Semiconductor.

0 kommentar(er)

0 kommentar(er)